引言

信號完整性是指電路系統中信號的質量。如果在要求的時間內,信號能夠不失真地從源端傳送到接收端,就稱該信號是完整的。隨著半導體工藝的迅猛發展、IC開關輸出速度的提高,信號完整性問題(包括信號過沖與下沖、振鈴、反射、串擾、地彈等)已成為高速PCB設計必須關注的問題之一。通常,數字邏輯電路的頻率達到或超過50 MHz,而且工作在這個頻率上的電路占整個系統的1/3以上,就可以稱其為高速電路。實際上,與信號本身的頻率相比,信號邊沿的諧波頻率更高,信號快速變化的跳變(上升沿與下降沿)引發了信號傳輸的非預期效果。這也是信號完整性問題的根源所在。因此,如何在高速PCB設計過程中充分考慮信號完整性因素,并采取有效的控制措施,提高電路設計質量,是必須考慮的問題。

借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法,可以發現信號完整性問題,根據仿真結果在信號完整性相關問題上做出優化的設計,從而達到提高設計質量,縮短設計周期的目的。

1 應用設計實例

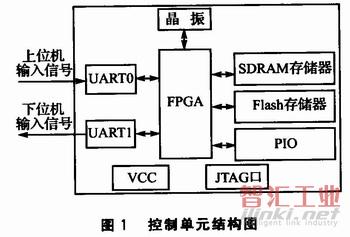

本文設計的控制單元在整個系統中的功能是將地面接收裝置接收到的編碼信號傳回給主站數據處理中心。具體工作過程是,首先存儲上位機數據,然后通過誤碼率測試與計算,選擇一條誤碼率最低的路徑作為數據傳輸路徑,最后將存儲的上位機數據通過該路徑傳輸到主站數據處理中心進行處理。經過綜合考慮,選用了Altera公司的Cyclone II-2C8作為核心芯片,以及外部擴展的SDRAM、Flash、各種輸入/輸出電路和MAX232接口芯片等,并結合Nios II軟核處理器開發套件實現。該控制單元結構如圖1所示。

CycloneII-2C8的時鐘頻率高達150 MHz以上,由于FPGA內部數據存儲區比較小,所以用SDRAM擴展了外部數據存儲空間。SDRAM采用了Hy-nix公司的HY57V651610/SO,時鐘頻率達到75 MHz以上。因此,必須考慮由于信號頻率過高引起的信號完整性問題。選擇了功能強大的Cad-ence設計軟件,它將原理圖設計、PCB Layout、高速仿真分析集于一體,可以解決在設計的各個環節中所存在的與電氣性能相關的問題,大大提高了設計的成功率。

2 關鍵信號拓撲結構和仿真

此系統中頻率較高的部分為FPGA和SDRAM,FPGA的時鐘頻率可達150 MHz以上,SDRAM可達75MHz以上。因為FPGA的內部高頻對其他器件沒有影響,而FPGA與SDRAM之間的連接為無縫連接,信號完整性的好壞直接影響著FPGA能否對SDRAM進行正確的讀和寫。PCB設計中,采用Cadence軟件的高速仿真工具SPECCTRAQuest,并利用器件的 IBIS模型來分析信號完整性,對阻抗匹配以及拓撲結構進行優化設計,以保證系統正常工作。本文只對信號反射和串擾進行詳細的講解,其他仿真與此類似。

2.1 反射

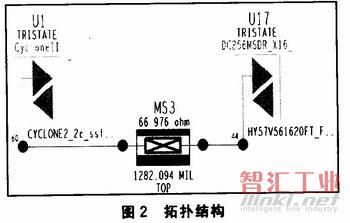

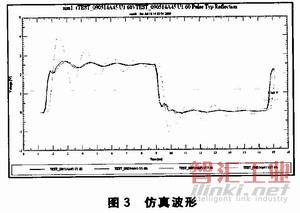

發射端為HY57V561620的44引腳,接收端為Cyclone II的60引腳,激勵為66 MHz的方波。圖2為拓撲結構,圖3為仿真波形。

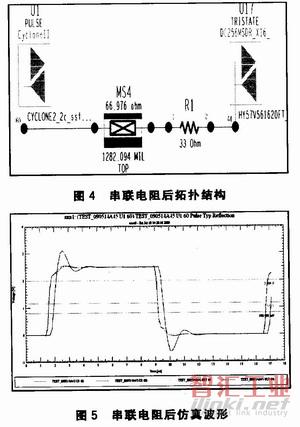

由仿真波形可以看出,由信號反射引起了波形畸變,產生了明顯的振鈴現象。振鈴現象的存在,使信號多次跨越電平邏輯門限從而導致邏輯功能紊亂。減小振鈴噪聲的一種有效手段是在電路中串聯一個小電阻,該電阻為電路提供了阻尼,能顯著減小振鈴幅度,縮短振鈴震蕩時間,同時幾乎不影響電路速度。在工程使用上,該電阻通常為33 Ω。串聯電阻后的拓撲結構和仿真波形如圖4和圖5所示。

串聯電阻后振鈴現象得到了很好的解決,實際上這個解決方法叫阻抗匹配,阻抗在信號完整性問題中占據著極其重要的地位。

2.2 串擾

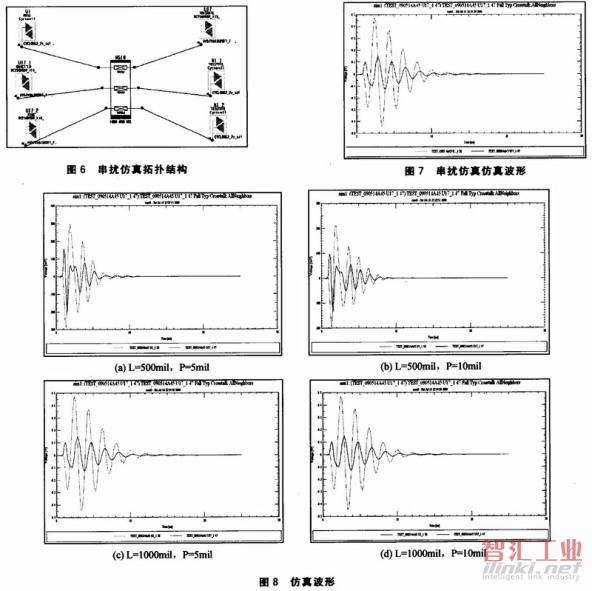

提取SD_DQlO(連接Cyclone II的59引腳和HY57V561620的45引腳),SD_DQll(連接Cyclone II的58引腳和HY57V561620的47引腳),SD_DQ-l2(連接CycloneII的57引腳和HY57V561620的48引腳)這三個網絡來做它們之間的串擾仿真。其中,SD_DQll作為被攻擊網絡,SD_DQlO和SD_D-Ql2作為攻擊網絡。它們的拓撲結構和仿真波形如圖6、圖 7所示(傳輸線的并行耦合長度L=1000 mil,間距P=5 mil)。

仿真波形如圖8所示。由圖7可以看出串擾對于被攻擊網絡的影響還是很大的,串擾值Crosstalk=657.95 mV串擾的大小與傳輸線的并行耦合長度L和間距P有關,耦合長度越短,間距越大,串擾就越小。仿真結果如表1所列。

因此,制作PCB時,在允許的情況下要盡可能減小不同性質信號線之間的并行長度,加寬它們之間的間距,改變某些線的線寬和高度。當然,影響串擾的因素還有許多,比如電流流向、干擾源信號頻率上升時間等,應綜合考慮。

結語

在本次控制單元高速PCB設計中,運用功能強大的Cadence軟件,從制作原理圖、PCB布局到高速仿真分析,取得了較好的效果。依據 SPEECTRAQuest仿真分析所得到的合理的拓撲結構和布局布線,使電路板工作正常。這種設計方式大大縮短了硬件調試時間,提高了工作效率,節約了設計成本。

(審核編輯: 智匯小新)

分享