無論是用離散邏輯、可編程邏輯,還是用全定制硅器件實現(xiàn)的任何數(shù)字設計,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓或制造工藝的偏差情況下將導致錯誤的行為,并且調(diào)試困難、花銷很大。 在設計PLD/FPGA時通常采用幾種時鐘類型。時鐘可分為如下四種類型:全局時鐘、門控時鐘、多級邏輯時鐘和波動式時鐘。多時鐘系統(tǒng)能夠包括上述四種時鐘類型的任意組合。

1.全局時鐘

對于一個設計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預測的時鐘。在PLD/FPGA設計中最好的時鐘方案是:由專用的全局時鐘輸入引腳驅(qū)動的單個主時鐘去鐘控設計項目中的每一個觸發(fā)器。只要可能就應盡量在設計項目中采用全局時鐘。PLD/FPGA都具有專門的全局時鐘引腳,它直接連到器件中的每一個寄存器。這種全局時鐘提供器件中最短的時鐘到輸出的延時。

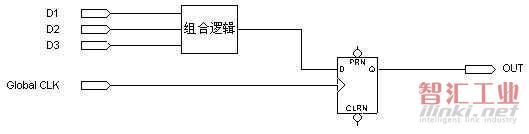

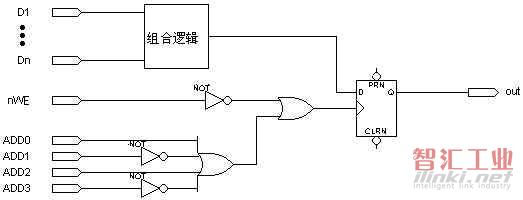

圖1 示出全局時鐘的實例。圖1 定時波形示出觸發(fā)器的數(shù)據(jù)輸入D[1..3]應遵守建立時間和保持時間的約束條件。建立和保持時間的數(shù)值在PLD數(shù)據(jù)手冊中給出,也可用軟件的定時分析器計算出來。如果在應用中不能滿足建立和保持時間的要求,則必須用時鐘同步輸入信號(參看下一章“異步輸入”)。

圖1 全局時鐘

(最好的方法是用全局時鐘引腳去鐘控PLD內(nèi)的每一個寄存器,于是數(shù)據(jù)只要遵守相對時鐘的建立時間tsu和保持時間th)

2.門控時鐘

在許多應用中,整個設計項目都采用外部的全局時鐘是不可能或不實際的。PLD具有乘積項邏輯陣列時鐘(即時鐘是由邏輯產(chǎn)生的),允許任意函數(shù)單獨地鐘控各個觸發(fā)器。然而,當你用陣列時鐘時,應仔細地分析時鐘函數(shù),以避免毛刺。

通常用陣列時鐘構成門控時鐘。門控時鐘常常同微處理器接口有關,用地址線去控制寫脈沖。然而,每當用組合函數(shù)鐘控觸發(fā)器時,通常都存在著門控時鐘。如果符合下述條件,門控時鐘可以象全局時鐘一樣可靠地工作:

1.驅(qū)動時鐘的邏輯必須只包含一個“與”門或一個“或”門。如果采用任何附加邏在某些工作狀態(tài)下,會出現(xiàn)競爭產(chǎn)生的毛刺。

2.邏輯門的一個輸入作為實際的時鐘,而該邏輯門的所有其它輸入必須當成地址或控制線,它們遵守相對于時鐘的建立和保持時間的約束。

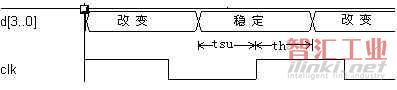

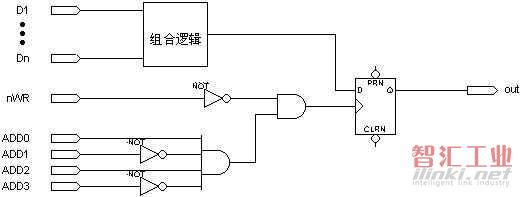

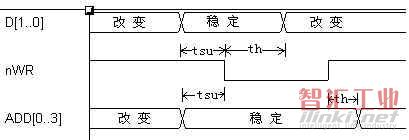

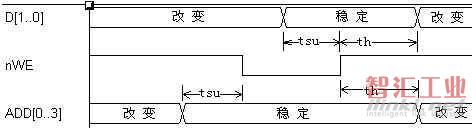

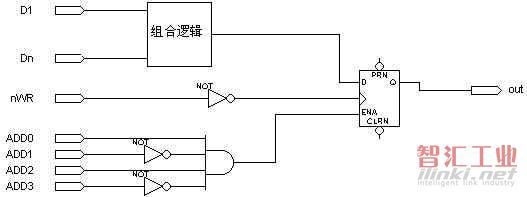

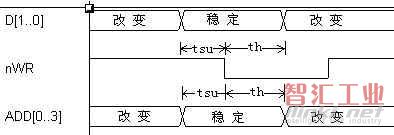

圖2和圖3 是可靠的門控時鐘的實例。在 圖2 中,用一個“與”門產(chǎn)生門控時鐘,在 圖3 中,用一個“或”門產(chǎn)生門控時鐘。在這兩個實例中,引腳nWR和nWE考慮為時鐘引腳,引腳ADD[o..3]是地址引腳,兩個觸發(fā)器的數(shù)據(jù)是信號D[1..n]經(jīng)隨機邏輯產(chǎn)生的。

圖2 “與”門門控時鐘

圖3 “或”門門控時鐘

圖2和圖3 的波形圖顯示出有關的建立時間和保持時間的要求。這兩個設計項目的地址線必須在時鐘保持有效的整個期間內(nèi)保持穩(wěn)定(nWR和nWE是低電平有效)。如果地址線在規(guī)定的時間內(nèi)未保持穩(wěn)定,則在時鐘上會出現(xiàn)毛刺,造成觸發(fā)器發(fā)生錯誤的狀態(tài)變化。另一方面,數(shù)據(jù)引腳D[1..n]只要求在nWR和nWE的有效邊沿處滿足標準的建立和保持時間的規(guī)定。

我們往往可以將門控時鐘轉(zhuǎn)換成全局時鐘以改善設計項目的可靠性。圖4 示出如何用全局時鐘重新設計 圖2 的電路。地址線在控制D觸發(fā)器的使能輸入,許多PLD設計軟件,如MAX PLUSII軟件都提供這種帶使能端的D觸發(fā)器。當ENA為高電平時,D輸入端的值被鐘控到觸發(fā)器中:當ENA為低電平時,維持現(xiàn)在的狀態(tài)。

圖4 “與”門門控時鐘轉(zhuǎn)化成全局時鐘

圖4 中重新設計的電路的定時波形表明地址線不需要在nWR有效的整個期間內(nèi)保持穩(wěn)定;而只要求它們和數(shù)據(jù)引腳一樣符合同樣的建立和保持時間,這樣對地址線的要求就少很多。

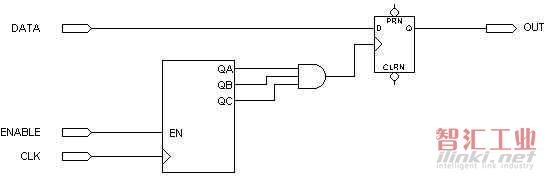

圖5給出一個不可靠的門控時鐘的例子。3位同步加法計數(shù)器的RCO輸出用來鐘控觸發(fā)器。然而,計數(shù)器給出的多個輸入起到時鐘的作用,這違反了可靠門控時鐘所需的條件之一。在產(chǎn)生RCO信號的觸發(fā)器中,沒有一個能考慮為實際的時鐘線,這是因為所有觸發(fā)器在幾乎相同的時刻發(fā)生翻轉(zhuǎn)。而我們并不能保證在PLD/FPGA內(nèi)部QA,QB,QC到D觸發(fā)器的布線長短一致,因此,如圖5 的時間波形所示,在器從3計到4時,RCO線上會出現(xiàn)毛刺(假設QC到D觸發(fā)器的路徑較短,即QC的輸出先翻轉(zhuǎn))。

圖5 不可靠的門控時鐘

(定時波形示出在計數(shù)器從3到4改變時,RCO信號如何出現(xiàn)毛刺的)

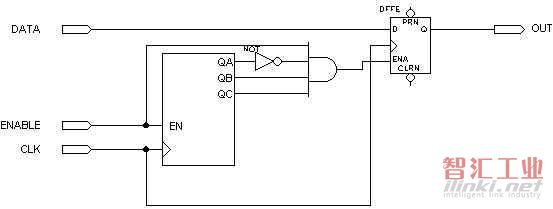

圖6 給出一種可靠的全局鐘控的電路,它是圖5不可靠計數(shù)器電路的改進,RCO控制D觸發(fā)器的使能輸入。這個改進不需要增加PLD的邏輯單元。

圖6 不可靠的門控時鐘轉(zhuǎn)換為全局時鐘

(這個電路等效于圖5電路,但卻可靠的多)

(審核編輯: 智匯胡妮)

分享