1 引言

在工業控制、質量檢測、虛擬儀器等場合,都需要采集數據并傳輸到上位機做分析處理。在傳輸數據時,有各種各樣的傳輸協議。傳統的RS232總線、RS485總線、CAN總線傳輸距離遠,但是其最大傳輸速度分別為12.8Mbps,10Mbps和1Mbps,無法滿足數據高速傳輸的需要。常用的USB接口和1394接口傳輸速度高,但是其理論傳輸距離分別只有5m和10m,無法滿足工業現場對遠距離傳輸的要求。為解決傳輸距離與傳輸速度之間的矛盾,設計了一種基于千兆以太網的高速數據采集系統。

2 系統總體設計方案

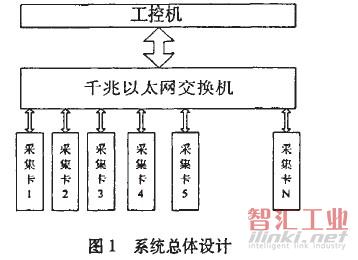

在電纜局部放電檢測系統中,需要采集因電纜局部放電而產生的高速脈沖信號并高速遠距離傳輸給上位機做分析處理。系統由工控機、千兆以太網交換機和數據采集卡三部分構成。

圖1為本系統總體設計框圖。

工控機作為上位機控制整個系統,通過向各個數據采集卡發送命令和各種采集參數控制采集卡的工作方式;對從數據采集卡傳輸上來的高速脈沖信號做分析處理,實現對放電量、放電相位、放電次數等各種局部放電參數的檢測;并顯示工頻周期放電圖、二維及三維放電譜圖。千兆以太網交換機用于工控機和多個數據采集卡交換數據。根據需要,可以通過交換機的級連從而增加采集卡的數量。數據采集卡安放在被檢測電纜旁,被檢測電纜每隔500米設置一個節點,每個節點兩側各放置3個采集卡對三相放電高速脈沖信號進行采集。系統以千兆以太網為中心,通過增加采集卡的數量,可以增大現場檢測范圍。

數據采集卡使用雙通道高速并行采集脈沖信號。

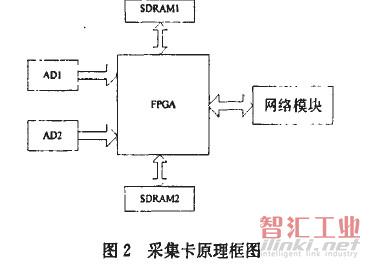

圖2為數據采集卡的原理框圖。

FPGA是數據采集卡的核心,接收上位機的命令,完成對輸入信號的接收,緩存并從緩存中取出數據發送給網絡模塊。

網絡模塊承接上位機與FPGA,采用千兆以太網傳輸技術,是數據采集卡的關鍵。

3 信號的接收

系統采用寬頻帶檢測技術,應用雙傳感器定向耦合脈沖信號,要求數據采集卡實現雙通道高速同步采集、雙通道同步偏差不超過5ns。由于待采集的放電脈沖信號的最高頻率可達30MHZ,根據采樣定理和實際經驗,采集卡的模數轉換器采樣率須達到IOOMSPS,才能很好地對信號進行復原和檢測。為滿足這種要求,模數轉換器采用2片AD9433。

AD9433是模擬器件公司生產的一種12位單片采樣A/D轉換器。它具有片上跟蹤/保持電路,轉換速率高達125MSPS。

對于許多應用場合,不需要外部基準和驅動元件。用戶可以選擇片上專有電路,可以極好地優化無雜散噪聲動態范圍(SFDR)。編碼時鐘支持差分或單端輸入,輸出為二進制或二進制的補碼格式。

A/D轉換器對用戶提供的取樣時鐘都十分敏感,跟蹤保持電路實質上是一個混頻器,任何的噪聲、失真或者時鐘的抖動都很影響A/D輸出的信號。由于這個原因,對AD9433的時鐘信號輸入的設計必須相當重視。FPGA的輸入時鐘源為24M,經過內部鎖相環倍頻后,由PLL專用輸出管腳輸出為AD9433提供干凈的時鐘源。

由于是高速模數混合電路,在設計印刷電路板時,布局布線是很講究的,應遵循以下原則:

(1)為減小數字電路的干擾,應將模擬電路和數字電路分開布局;

(2)對于時鐘線、差分線等對干擾很敏感的信號線走線時必須使用3W原則;

(3)對于高速信號線要考慮傳輸線效應,注意阻抗匹配;

(4)信號線走線時要盡可能減少電流環路的面積,以避免形成大的環狀天線;

(5)電路板只采用一個參考平面,避免形成偶極天線;

(6)為減小信號線上的分布電阻、電容和電感,應盡量縮短走線長度和增大導線間的距離。

4 數據的緩存

每個AD需要連續采集16M×12bit的數據傳輸給上位機軟件進行分析計算,2片AD同部采集的數據量共48MByte。

在AD前端100M高速采樣率下,為使如此大量數據無誤傳輸,數據緩存設計非常必要。

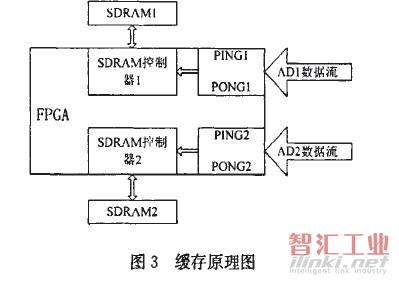

圖3為緩存部分設計原理圖。

主控芯片FPGA選用ALTERA的EPlCl2Q240,片上帶有2個專用的PLL,12060個LE,內部RAM資源多達239616bit。在市場上存在多類存儲器,包括靜態隨機存儲器SRAM,同步動態隨機存儲器SDRAM,雙倍速率SDRAM(DDRSDRAM)等。由于SRAM容量小,DDRSDRAM控制復雜,系統選用2片IS42s32800作緩存芯片,一片SDRAM緩存一個通道的數據。

IS42:532800是一片8M×32bit的SDRAM,最高工作頻率為166M,3.3V供電。它包含以下幾個操作:初始化操作、讀出數據操作、寫入數據操作、刷新操作。

程序設計時,在FPGA內部開辟4個512×12位的雙口R—蝴暫存高速數據進行乒乓操作。FPGA把AD輸出的數據寫入到乒RAM中的同時,又把RAM中的數據讀出寫入到SDRAM,這樣前端的數據流便不會中斷,提高了數據傳輸速度。AD采樣頻率為100MSPS,為使SDRAM能無誤存儲數據,則SDRAM必須在IOOMHZ的時鐘頻率下工作。這對FPGA的時序設計和PCB的設計是一個考驗,為了使系統能夠更加穩定地工作,對SDRAM的控制采用了降頻設計技術。FPGA把12bit的AD輸出數據轉化成24bit的數據輸出給SDRAM,這樣SDRAM只需工作在50MHZ的時鐘頻率下就能無誤存取數據,大大提高了系統的穩定性。

5 網絡傳輸

以太網技術是當今應用最為廣泛的網絡技術。千兆以太網技術繼承了以往以太網技術的許多優點,同時又具有許多新的特性,例如傳輸介質包括光纖和銅纜,使用8B/lOB的編解碼方案,采用載波擴展和分組突發技術等。將千兆以太網應用到高速數據采集系統中是一個趨勢。

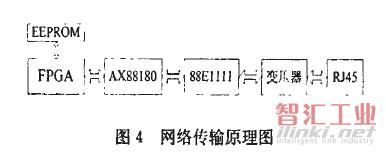

圖4是網絡傳輸模塊原理圖。

數據鏈路層芯片AX88180是臺灣ASIX公司推出的一款高性能低成本的Non-PCI千兆以太網控制器,符合IEEES02.3/IEEE 802.3u/IEEE 802.3ab協議,適用于多種需要高速接入網絡的嵌入式系統。Ax88180內置10/100/1000Mb/s以太網媒體存取控制器(MAC);內置主機接口控制器,可以與16/32位主機方便連接,尋址方式與SRAM相同;內置40KB的SRAM網絡封包緩存器,其中32kB用于從PHY接收數據包,8KB用于主機發送數據包到PHY,可以用高效方式進行封包的存儲、檢索與修改;內置256字節的配置寄存器,用于主機控制和參數設置。物理層芯片采用88E1111。AX88180與88E1111之間采用RGMII接口方式互連,負責數據傳送底層協議的實現。

UDP和TCP協議都屬于OSI(開放系統互連)參考模型的傳輸層協議。雖然TCP協議中植入了各種安全保障功能,但是在實際執行的過程中會占用大量的系統開銷,無疑使速度受到嚴重的影響。反觀UDP由于排除了信息可靠傳遞機制,將安全和排序等功能移交給上層應用來完成,極大降低了執行時間,使速度得到了保證,包括網絡視頻會議系統在內的眾多的客戶/N務器模式的網絡應用都使用UDP協議。為達到高速傳輸的目的,系統采用UDP/ho協議,并使用FPGA實現。為了便于上位機對采集卡進行管理,FPGA根據上位機的要求,修改采集卡的IP地址,并把IP地址存儲到EEPROM中。

6 結語

本系統把高速數據采集技術和千兆以太網技術有機結合起來,實現了數據高速采集并遠距離高速傳輸功能。

由于系統工作在復雜電磁環境中,在設計PCB時就考慮了EMI和EMC等問題,系統抗干擾能力強。經過驗證,采集卡接收到上位機的采集命令后,實現了雙通道同時采、每通道100MSPS的采集速度;采集數據完畢后,采集卡向上位機的數據傳輸速度可達300Mbit/S。在交換機上隨意增加采集卡的數量,系統能正常工作。

(審核編輯: 智匯小新)

分享